Ah, there's a bit of confusion because that was two rumored "secret sauces" that Cerny in his infinite wisdom had chosen from AMD's roadmap that would help the PS5 perform much higher than its variable CPU and 10TF, both involving L3.

One was Zen3's unified cache that ended not happening and L3 cache for the GPU, that it looks like it happened but by an irrelevant degree.

I'm shutting down console war nonsense. PS5 fanboys are doing the exact some nonsense Xbox fanboys did when it turned out the Xbox One was a less powerful system than the PS4 last time around. There's no secret sauces yet to be found, we have known the full specs of both systems for months/years at this point.

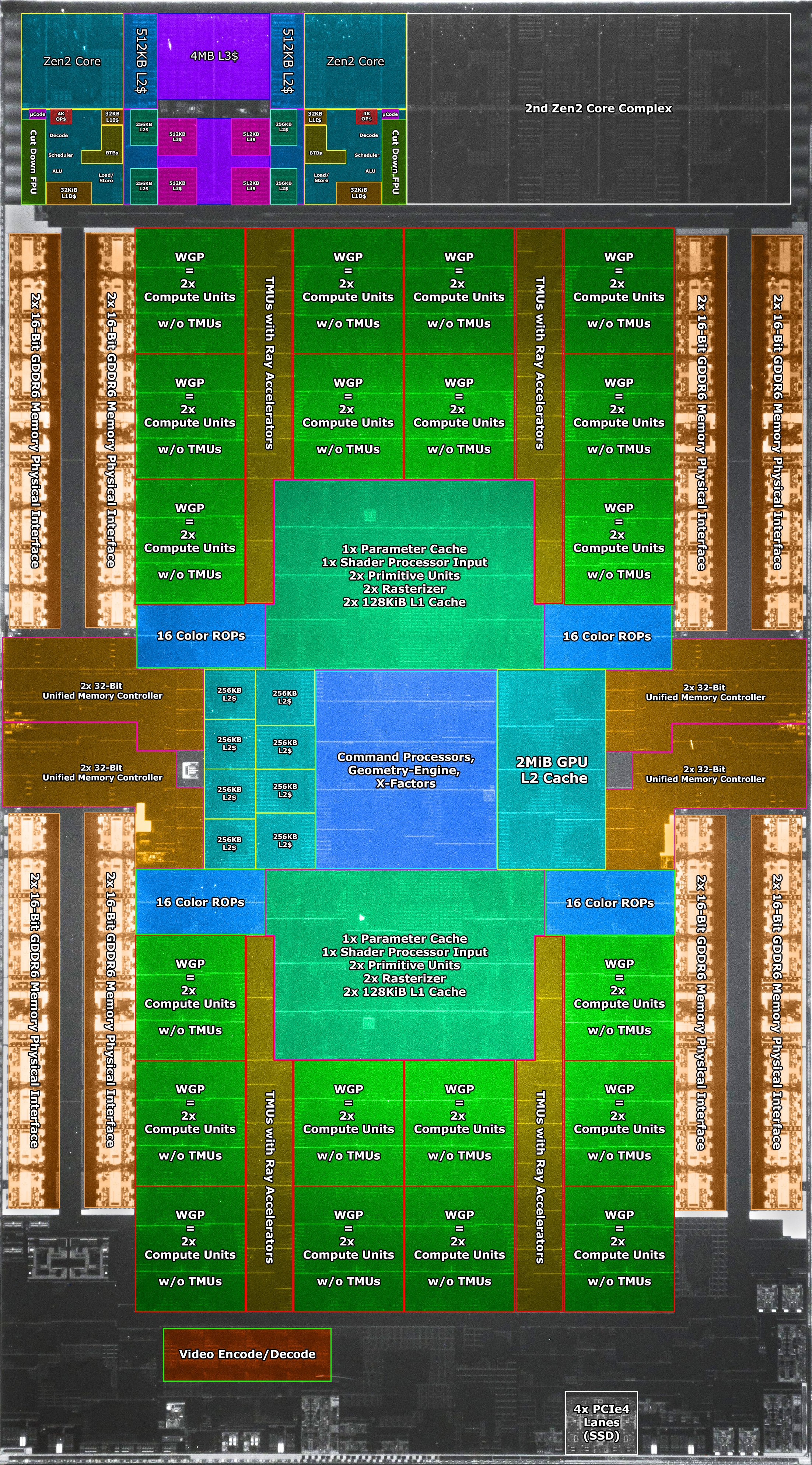

The situation is actually the inverse! The "second GPU" does actually exists here!

The thing that people should take away from all this is that all these little features that each company puts on their machines helps little and may makes little difference in practice all things considered.

IF helps achieve a higher effective bandwidth, but can't the same be achieve by a more traditional way, just using more memory channels or faster memory? The amount of IF there is very small so in practice we can't think like if the PS5 have more effective bandwidth than the SEX (but is should help with latency, that was none of Cerny's goals?).